#208 November 2007

# THE OFFICE OFFIC

# THE MAGAZINE FOR COMPUTER APPLICATIONS ANALOG TECHNIQUES

Switch Analog & VoIP Calls

DDS RF Signal Generator

SMT Manufacturing Basics

iEthernet Bootcamp

# The NetBurner Eclipse Ethernet Development Kit

Only \$99

#### Featuring NetBurner's Eclipse IDE!

One Click Compile and Load | Intelligent Code Completion | Integrated Debugger

#### **The Complete Hardware and Software Solution**

Includes NetBurner MOD5270 Ethernet Core Module Performance and Memory | 32-Bit CPU | Freescale ColdFire MCF5270 147Mhz | 512K Flash Memory | 2MB SDRAM Device Connectivity | 10/100 Ethernet | 3 UARTs | I<sup>2</sup>C | SPI | 47 Digital I/O | SD/MMC Flash Card Support

> **Communication Software** TCP/IP Stack | HTTP Web Server | FTP | E-Mail | PPP | Flash File System

> **Development Software** NB Eclipse IDE | Graphical Debugger | Deployment Tools | Examples

> > **System Software** µC/OS RTOS | ANSI C/C++ Compiler and Linker

### etBurner.com

Product No. | NNDK-MOD5270LC-KIT Information and Sales | sales@netburner.com Telephone | 1-800-695-6828

# It's showtime.

#### Get Your Ticket to the Ultimate Embedded Design Starter Kit.

Fixed-function microcontrollers had their share of the spotlight. It's time for a revolutionary—and simplified—approach to embedded application development. Get a Cypress PSoC<sup>®</sup> FirstTouch<sup>™</sup> Starter Kit now and discover how much PSoC mixed-signal arrays—powerful, programmable analog and digital blocks, embedded memory and a fast MCU—shorten your time-to-market. This kit includes the easy-to-use PSoC Express<sup>™</sup> visual embedded system design tool, and gives you embedded designs you can evaluate right out of the box. Get yours and step into the spotlight today.

Includes four ready-to-use mixed-signal applications on a single platform.

Buy your PSoC FirstTouch Ultimate Starter Kit now at: www.cypress.com/go/FirstTouch

Buy Now \$29.95\*

HRSTIQUCH

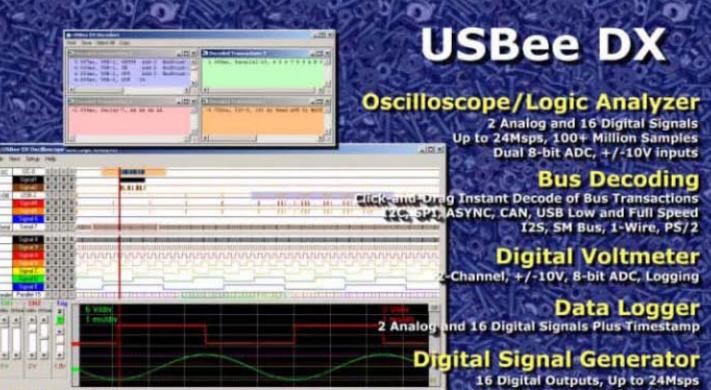

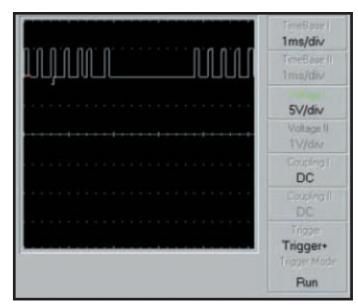

Link Instruments (973) 808-8990

www.Linkins4.com

Note the date!

# Nuremberg, Germany **February 26 – 28, 2008 embedded world** 2008 Exhibition & Conference Nürnberg

...it´s a smarter world

www.embedded-world.de

Exhibition organizer NürnbergMesse Tel +49(0)911.8606-0 info@nuernbergmesse.de Conference organizer DESIGN&ELEKTRONIK Tel +49(0)8121.95-1340 cgrote@design-elektronik.de

#### Media partners

elektronik report

#### DESIGN& ELEKTRONIK

automotive

elektronik net.de

#### Elektronik

NÜRNBERG MESSE

# TASK MANAGER CIRCUIT CELLA

#### New Initiatives

enjoy attending conferences because I get to leave the editorial office and meet face to face with our readers, writers, advertisers, and contest sponsors. In September, I drove to the Embedded Systems Conference in Boston. As usual, I had a great time meeting with everyone who stopped by our booth.

This year's conference was important for a few reasons. Most notably, we launched two new exciting initiatives: the WIZnet iEthernet Design Contest 2007 and a call for articles about "intelligent energy" (IE) solutions.

As for the WIZnet contest, check out Fred Eady's contest primer on page 34. Fred introduces you to the power of the WIZnet W5100 hardwired TCP/IP Ethernet controller. If you're inspired, you can easily join the Ethernet revolution at www.circuitcellar.com/wiznet/. Registering for for a project number will take only a few minutes. With \$15,000 in total cash prizes up for grabs, it's well worth the effort.

Next month, we will run a new section of the magazine called Intelligent Energy (IE) Solutions. To kick things off, the new section will feature Part 1 of Steve Ciarcia's series about his new photovoltaic (PV) installation. As you know, Steve has mentioned his PV system in his monthly Priority Interrupt columns. Next month, you'll get to read about the details.

The purpose of the IE section is to highlight exciting new designs that address topics such as solar-powered systems, energy-efficient embedded designs, and power-saving applications. As many of you learned in Boston, we're challenging you to draw up an IE design, build a system, and send us an article proposal. If your proposal intrigues us, we might ask you to submit an article for this new section. Are you up for the challenge?

As you prepare to enter the WIZnet contest or start an IE design (or both), be sure to read through this issue's batch of compelling articles. Our authors cover a wide variety of well-designed applications.

On page 12, David Rowe describes how he combined his interest in embedded systems and telephony to design a µClinux-powered IP-PBX. If you follow his lead, you too will be able to switch analog and VoIP calls

Want to know what it took to win a top prize in the Luminary Micro DesignStellaris2006 Contest? Check out Thomas Alldread's versatile NimbleSig design on page 22.

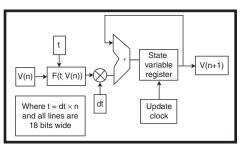

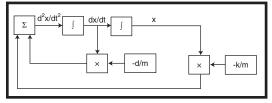

In his well-known ECE 576 course at Cornell University, Bruce Land and his students use FPGAs to build embedded systems. In "Hybrid Computing on an FPGA" (p. 44), Bruce explains how he simulates the parallel functions of an analog computer on an FPGA.

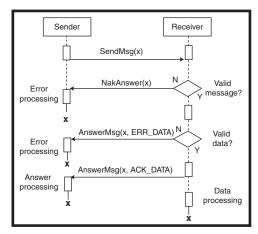

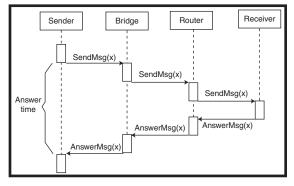

Because we like variety, the second half of this issue features articles on topics that are a bit less hardware-centric: communication protocols (p. 50), software design techniques for small embedded systems (p. 58), and product development (p. 63). We're confident that the advice provided in these three articles will serve you well as you start your next project. Good luck!

cj@circuitcellar.com

C.apite

FOUNDER/EDITORIAL DIRECTOR Steve Ciarcia

MANAGING EDITOR C.J. Abate

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Jeff Bachiochi Ingo Cyliax Robert Lacoste George Martin Ed Nisley

NEW PRODUCTS EDITOR John Gorsky

**PROJECT EDITORS** Steve Bedford Ken Davidson David Tweed

ASSOCIATE EDITOR Jesse Smolin

CHIEF FINANCIAL OFFICER Jeannette Ciarcia

> MEDIA CONSULTANT Dan Rodrigues

CUSTOMER SERVICE Debbie Lavoie

> CONTROLLER Jeff Yanco

ART DIRECTOR KC Prescott

GRAPHIC DESIGNER Mary (Turek) Sobuta

> STAFF ENGINEER John Gorsky

**ADVERTISING**

```

860.875.2199 • Fax: 860.871.0411 • www.circuitcellar.com/advertise

```

#### PUBLISHER

Sean Donnelly Direct: 860.872.3064, Cell: 860.930.4326, E-mail: sean@circuitcellar.com

ADVERTISING REPRESENTATIVE Shannon Barraclough Direct: 860.872.3064, E-mail: shannon@circuitcellar.com

ADVERTISING COORDINATOR Valerie Luster E-mail: val.luster@circuitcellar.com

> Cover photography by Chris Rakoczy-Rakoczy Photography www.rakoczyphoto.com

#### PRINTED IN THE UNITED STATES CONTACTS

SUBSCRIPTIONS

Information: www.circuitcellar.com/subscribe\_E-mail: subscribe@circuitcellar.com Subscribe: 800.269.6301, www.circuitcellar.com/subscribe, Circuit Cellar Subscriptions, P.O. Box 5650. Hanover, NH 03755-5650

Address Changes/Problems: E-mail: subscribe@circuitcellar.com

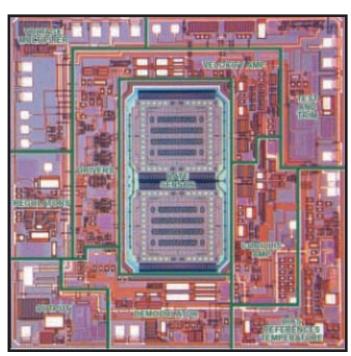

#### GENERAL INFORMATION

860.875.2199, Fax: 860.871.0411, E-mail: info@circuitcellar.com

Editorial Office: Editor, Circuit Cellar, 4 Park St., Vernon, CT 06066, E-mail: editor@circuitcellar.com

New Products: New Products, Circuit Cellar, 4 Park St., Vernon, CT 06066, E-mail: newproducts@circuitcellar.com AUTHORIZED REPRINTS INFORMATION

#### 860.875.2199. E-mail: reprints@circuitcellar.com AUTHORS

Authors' e-mail addresses (when available) are included at the end of each article.

CIRCUIT CELLAR®, THE MAGAZINE FOR COMPUTER APPLICATIONS (ISSN 1528-0608) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Vernon, CT 06066. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$23.95, Canada/Mexico \$34.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$43.95, Canada/Mexico \$59.95, all other countries \$85. All subscription orders payable in U.S. funds only via Visa, MasterCard, international postal money order, or check drawn on U.S. bank. Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 5650, Hanover, NH 03755-5650 or call 800.269.6301

Postmaster: Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 5650, Hanover, NH 03755-5650.

Circuit Cellar® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of rear erassembled projects, Circuit Cellar® disclaims any responsibility for the sale and proper function of reader-assembled projects based upon or from plans, descriptions, or information published by Circuit Cellar®.

The information provided by Circuit Cellar® is for educational purposes. Circuit Cellar® makes no claims or warrants that readers have a right to The immation provided by Urcuit detailers for educational purposes. Urcuit detailer makes no cames or warrants that readers have a right build things based upon these ideas under patent or other relevant infelicular grouperly law in their jurisdicion, or that readers have a right to construct or operate any of the devices described herein under the relevant patent or other intellectual property law of the reader's jurisdiction. The reader assumes any risk of infringement liability for constructing or operating such devices.

Entire contents copyright @ 2007 by Circuit Cellar, Incorporated. All rights reserved. Circuit Cellar is a registered trademark of Circuit Cellar, Inc Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

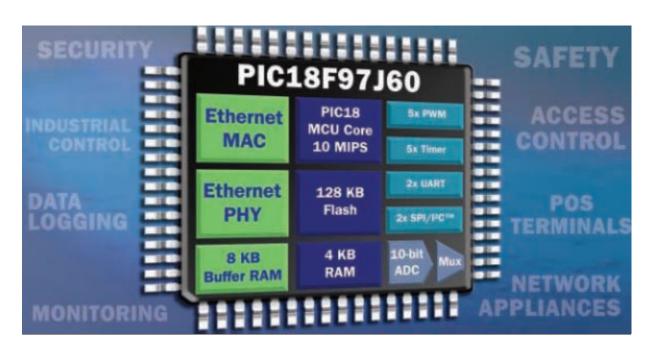

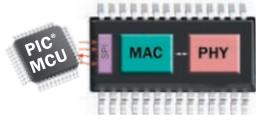

# **Embedded Ethernet Any Application, Any Location**

Monitor, control or re-program your application remotely with ease using the integrated Ethernet PIC18F97J60 family and **FREE** TCP/IP software.

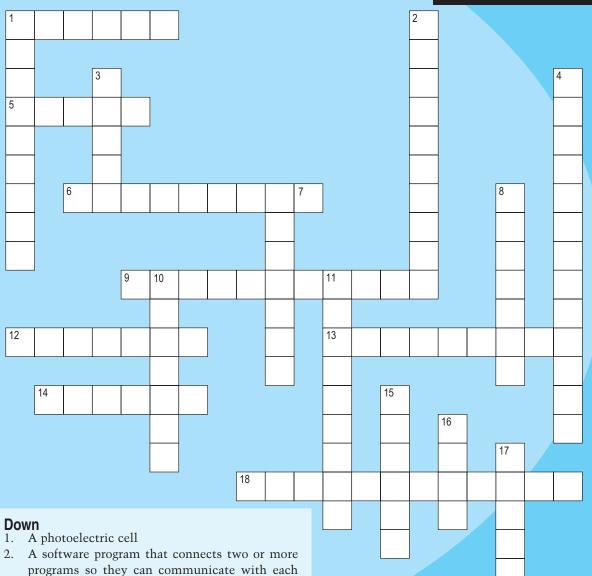

#### **GET STARTED IN 3 EASY STEPS**

at www.microchip.com/ethernet.

1. Learn about our Ethernet devices in 20 minutes

Take advantage of our Ethernet web seminars.

- **2.** Download our FREE TCP/IP software Our TCP/IP stack is available in source code for flexible and optimized code size.

- 3. Check out our low-cost Ethernet tools

Evaluate the PIC18F97J60 family with the PICDEM.net™ 2 Demo Board

available for only \$129.98

when you use coupon code

ETHTOOL during checkout at

www.microchipDIRECT.com.

| Purchase and program your<br>Ethernet PIC® microcontrollers<br>and related development tools at www.microchipdirect.com |      |               |                                                      |  |

|-------------------------------------------------------------------------------------------------------------------------|------|---------------|------------------------------------------------------|--|

| Device                                                                                                                  | Pins | Flash<br>(KB) | Features                                             |  |

| PIC18F97J60                                                                                                             | 100  | 128           | 10-BaseT Ethernet                                    |  |

| PIC18F87J60                                                                                                             | 80   | 128           | 12 KB RAM                                            |  |

| PIC18F67J60                                                                                                             | 64   | 128           | (8 KB dedicated<br>Ethernet)                         |  |

| PIC18F96J65                                                                                                             | 100  | 96            | 5x 16-bit timers                                     |  |

| PIC18F86J65                                                                                                             | 80   | 96            | 10-bit ADC, 16 channels                              |  |

| PIC18F66J65                                                                                                             | 64   | 96            | 2 analog comparators                                 |  |

| PIC18F96J60                                                                                                             | 100  | 64            | 2 UART with LIN protocol                             |  |

| PIC18F86J60                                                                                                             | 80   | 64            | 2 SPI, 2 I <sup>2</sup> C™<br>Industrial Temperature |  |

| PIC18F66J60                                                                                                             | 64   | 64            | -40° to +85°C                                        |  |

| ENC28J60                                                                                                                | 28   | 8K RAM        | MAC, PHY, SPI Interface                              |  |

Visit www.microchip.com/ethernet for additional devices supporting connectivity solutions and related development tools, application notes, reference designs, web seminars and more!

Or you may consider...

Adding Ethernet to any application with Microchip's **ENC28J60** stand-alone Ethernet controller with full software support for PIC18, PIC24 and dsPIC® DSCs.

Microcontrollers • Digital Signal Controllers • Analog • Serial EEPROMs

# **November 2007: Analog Techniques**

#### **FEATURES**

- 12 Embedded IP-PBX Switch Analog and VoIP Calls David Rowe

- 22 NimbleSig A Compact DDS RF Signal Generator Thomas Alldread Second Prize Luminary Micro DesignStellaris2006 Contest

- 34 **iEthernet Bootcamp** Get Started with the W5100 Fred Eady WIZnet iEthernet 2007 Design Contest Primer

- 44 Hybrid Computing on an FPGA Bruce Land

- 50 **Communication Protocols** *Massimo Manca*

- 58 **Resilience in Embedded Designs (Part 3)** Software *Aubrey Kagan*

- 63 **SMT Manufacturing** Take a Board from Prototype to Production *Zack Gainsforth*

#### **COLUMNS**

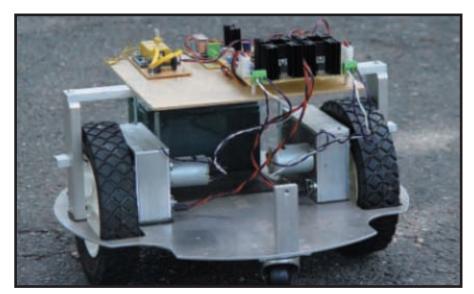

- 70 FROM THE BENCH Motor Driving for a Robotic Arm Jeff Bachiochi

- 76 LESSONS FROM THE TRENCHES A Flash in the Pan George Martin

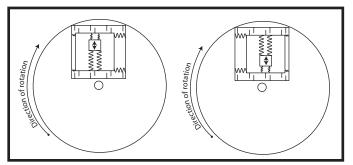

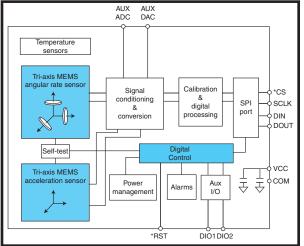

- 80 SILICON UPDATE Thanks for the MEMS Tom Cantrell

# Navigation in a Box (p. 80)

Embedded IP-PBX Design (p. 12)

Start a W5100-Based Project (p. 34)

#### **DEPARTMENTS**

- 4 **TASK MANAGER** New Initiatives *C.J. Abate*

- 8 NEW PRODUCT NEWS edited by John Gorsky

- 93 CROSSWORD

94 INDEX OF ADVERTISERS December Preview

#IZnet

96 **PRIORITY INTERRUPT** Let There Be Light *Steve Ciarcia*

# Go wireless with AVR Z-link

#### Get more at: www.atmel.com/AVRman

© 2007 Annie Corporation, All rights reasonal: Altrad<sup>®</sup> AVIP and togs are regarismed tradectarks of Annie Corporation or the subschafes. Other terms and product rightse may be tradectarity of others. All Characteric or this document are created by MyNe and Faretain Fabrican All 2007.

Edited by John Gorsky Visit www.circuitcellar.com/npn for more New Product News.

#### 2.7-W CONSTANT OUTPUT POWER CLASS-D AMPLIFIER

The **TPA2013D1** is a monolithic, filter-free, class-D audio power amplifier with an integrated boost converter that provides constant output power for portable applications such as personal navigation devices, PDAs, mobile phones, portable media players, and handheld gaming devices. The amplifier generates high output power from a low supply voltage without

distorting the audio and can also supply distorting the audio and can also supply the power of external devices. The device has a wide supply voltage operation of 1.8 to 5.5 V to simplify power supply design and allow for direct connection to the battery. The new device provides a maximum output power of 2.7 W across a 4- $\Omega$  load or 2.2 W across an 8- $\Omega$  load in addition to providing an adjustable constant output power of up to 1.5 W in the entire Lithium-Ion battery range of 2.3 to 4.8 V. This capability makes the audio output power insensitive to bat-

2.7-W, Class-D Audio Amplifier Provides Constant Output Power International Constant Power Note Internationa

tery voltage fluctuations, thereby maintaining audio quality and volume as the battery discharges.

Several key features of the TPA2013D1 help increase system audio quality. For example, all internal modules run off the same reference clock, silencing potential audible beat frequencies that could occur

when using a separate discrete amplifier and boost converter. The synchronized clock and very high power supply rejection ratio, 95 dB at 217 Hz, serve to further reduce noise in the system.

The WCSP costs **\$1.55** in 1,000-unit quantities and **\$1.45** for the QFN package.

Texas Instruments, Inc. www.ti.com

STATEMENT REQUIRED BY THE ACT OF AUGUST 12, 1970, TITLE 39, UNITED STATES CODE SHOWING THE OWNERSHIP, MANAGEMENT AND CIRCULATION OF CIRCUIT CELLAR, THE MAGAZINE FOR COMPUTER APPLICATIONS, published monthly at 4 Park Street, Vernon, CT 06066. Annual subscription price is \$23.95. The names and addresses of the Publisher, Editorial Director, and Managing Editor are: Publisher, Sean Donnelly, 4 Park Street, Vernon, CT 06066; Editorial Director, Steven Ciarcia, 4 Park Street, Vernon, CT 06066; Managing Editor, Carmine J. Abate, 4 Park Street, Vernon, CT 06066. The owner is Circuit Cellar, Inc., Vernon, CT 06066. The names and addresses of stockholders holding one percent or more of the total amount of stock are: Steven Ciarcia, 4 Park Street, Vernon, CT 06066. The owner is of copies of each issue during the preceding twelve months is: A) Total number of copies (net press run) 22,801; B) Paid/Requested circulation (1) Mail subscriptions: 9,327; (3) Sales through dealers and carriers, street vendors and counter sales: 5,249; C) Total paid/requested circulation: 14,576; D) Nonrequested distribution: 4,499; F) Total distribution: 19,075; G) Copies not distributed: 3,726; H) Total: 22,801; (I) Percent paid/requested: 76.4%. Actual number of copies of the single issue published nearest to filing date (October 2007, Issue #207); A) Total number of copies (net press run) 22,630; B) Paid/Requested circulation (1) Mail subscriptions: 9,658; (3) Sales through dealers and carriers, street vendors and counter sales: 5,173; (C) Total paid/requested circulation: 14,831; D) Nonrequested distribution (b) mail and outside the mail) (1) Outside county nonrequested distribution; 4,499; F) Total aid/requested circulation: 14,831; D) Nonrequested distribution (b) mail and outside the mail) (1) Outside county nonrequested (stribution; 8,148; F) Total distribution; 22,979; G) Copies not distributed: 3,651; H) Total: 26,630; (I) Percent paid/requested: 5,77; C) Total paid/requested circulation: 14,831; D) Nonrequested (stirbution; 8,148; F)

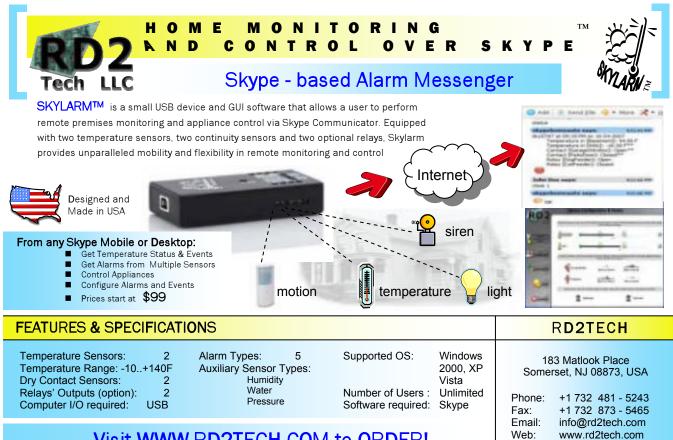

#### Visit WWW.RD2TECH.COM to ORDER!

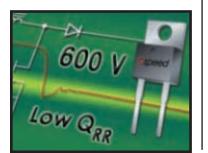

#### NEW RECTIFIERS BOOST PFC EFFICIENCY

The new **Q-Series** rectifier family of devices is designed specifically for use in power factor correction (PFC) circuits that deliver 200 to 1,000 W of power. Replacing an ultrafast diode with a Q-Series device typically realizes efficiency improvements of 0.5 to 1.5% in the boost converter stage, which are similar to those obtained by using exotic silicon carbide diodes. Developed using a proprietary technology, the Q-Series family of devices has the lowest reverse-recovery-charge  $(Q_{RR})$  and the best softness factor of any high-speed silicon rectifiers currently available on the market.

The Q-Series product family consists of three devices, which are rated to deliver continuous forward current values of 3, 5, and 8 A, respectively. The 3-A device (LQA03TC600) would typically be used in boost converter stages that deliver between 200 and 400 W of continuous output power. The 5-A device (LQA05TC600) would find its home in converters that deliver between 400 and 700 W,

while the zone for the 8-A device (LQA08TC600) is from about 700 to 1,000 W.

The LQA03TC600 costs **\$0.78** each, the LQA05TC600 costs **\$0.88** each, and the LQA08TC600 costs **\$1.08** each in 50,000-piece quantities.

Qspeed Semiconductor www.qspeed.com

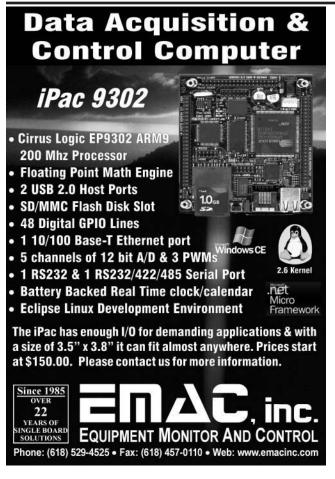

#### EASY-TO-PROGRAM LINUX CONTROLLER

The **Omniflash** controller provides users with a rich array of I/O devices seamlessly supported by a preinstalled Linux 2.4 kernel. The controller comes furnished with 10/100 Ethernet, two serial ports, a battery-backed clock/calendar, a USB, digital I/Os, and stereo audio line level outputs. The 200-MHz ARM9 processor handles complex multitasking operations efficiently. Onboard memory includes 16 MB of flash memory organized as an Ext2 file system and 32 MB of SDRAM.

The Linux operating system also includes more than 150 standard Linux/Unix system utilities including ftp, tftp, telnet, and vi. Also included in the development kit is a bootable Knoppix CD-ROM preconfigured with development tools to support the Omniflash.

The Omniflash controller costs **\$129** each in quantities of 100. Development kits are available for **\$199**.

JK microsystems, Inc. www.jkmicro.com

# <section-header> Wirespectation Operation Operation

Order Online At rabbitappkits.com

#### METRIC THREADED EMI FILTERS AVAILABLE IN FEED-THROUGH AND PI CIRCUITS

New **metric threaded EMI filters** from Spectrum Control include an M3 X 0.5 feed-through circuit and an M4 X 0.7 Pi circuit. These filters are easily mounted in a tapped hole or through-hole and have a hex head dimension across the flats of 4 mm. The metric threading makes these EMI filters ideal for design solutions in European and Asian markets.

Spectrum's metric threaded EMI filters have capacitance values ranging from 100 to 12,000 pF, a current rating of 10 A, a voltage rating of 100 VDC, and a dielectric withstanding voltage of 250 VDC. The durable resin-sealed case provides excellent environmental protection. They are primarily used in filtering signal/data lines, industrial controls, telecommunications, medical equipment, and test equipment.

equipment. The metric

threaded EMI filters cost from **\$2** to **\$5** depending on configuration and quantity, with a lead time of eight weeks.

#### Spectrum Control, Inc. www.specemc.com

#### NEW C COMPILER FOR PIC24 MCUs AND dsPIC DSCs

The **PCD** is a low-cost, quality 24-bit C compiler for the PIC24 MCUs and dsPIC DSCs. The compiler includes peripheral libraries for SPI, I<sup>2</sup>C, UART, RTC, input capture, and PWMs. The PCD includes new built-in functions and examples to aid in getting a project started.

CCS will also offer prototyping boards to aid in PIC24 and dsPIC DSC development. The DSP starter development kit features a dsPIC30F2010 prototyping board. The DSP starter development kit is a general-purpose development board including a potentiometer, a push button, three LEDs, an RS-232 level converter, and an ICD connector and header to access the dsPIC30F2010 chip. CCS will also offer two PIC24 development kits and DSP analog/audio development kits by the end of the year. The DSP analog/audio board will demonstrate the DSP features of the dsPIC by providing an example audio conditioning

board. Kits maybe purchased with a PCD compiler or as a board-only option.

The PCD is in the fundamental development period and is now available for sale. The PCD is offered as a commandline compiler for **\$250**, an add-on to an existing PCWH compiler for **\$150**, a stand-alone IDE compiler for **\$350**, and a full-version PCWHD compiler for **\$575**.

Custom Computer Services, Inc. www.ccsinfo.com

#### FAMILY OF HANDHELD DIGITAL MULTIMETERS

The **U1240A** series of digital multimeters enables field or facilities technicians and engineers to do more than just voltage, current, and resistance measurements. For instance, providing more than typical voltage measurements on switches, the U1240A series enables users to observe open/close switch behaviors in the presence of intermittent signals.

Users can also easily gauge the extent of transformer heating or the efficiency of refrigeration systems with the DMM's dual and differential temperature capabilities. This, coupled with its microamp measurement function, is especially handy for troubleshooting HVAC equipment and sensors.

When maintaining AC motors or troubleshooting circuit breakers that trip prematurely, the series helps users quickly verify the presence of harmonics that may have caused device overheating. With its internal memory, the DMM lets users conveniently perform data collection on the go for later analysis.

The U1240A series of handheld digital multimeters comprises two models: the U1241A and the U1242A. They are durable, safe, and easy to use. These DMMs simplify installation and maintenance by providing a broad range of measurement functions, including voltage, capacitance, and temperature. Key features include 10,000-count resolution, dual display, dual-intensity backlight, dual and differential temperature, harmonic ratio, a switch counter, and data logging.

The Agilent U1240A series also provides wider usage for higher resistance measurements (up to 100 M $\Omega$ ) and lower current measurements (down to 0.1 mA).

The Agilent U1240A series starts at \$200.

Agilent Technologies, Inc. www.agilent.com

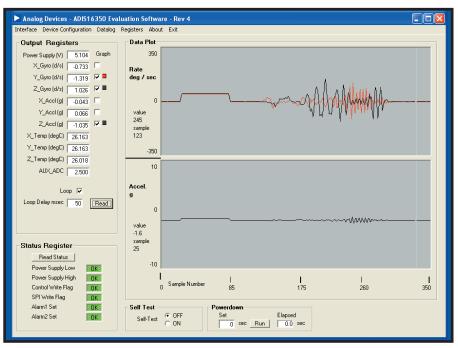

#### **10-MHz DIGITALLY PROGRAMMABLE INSTRUMENTATION AMPLIFIER**

Designed for data acquisition systems, automatic test equipment, and biomedical instruments requiring fast, accurate measurement with robust signal conditioning over large voltage ranges, the AD8253 digitally programmable instrumentation amplifier is able to reach gains of 1,000 while offering DC precision and AC bandwidth unmatched by other instrumentation amps or discrete solutions on the market. A large gain setting allows small signals, such as those from sensors, to be amplified to drive an ADC.

The AD8253 is digitally programmable with gain settings of 1, 10, 100, and 1,000, letting users adjust gain even after the devices are designed into the system. Operating from  $\pm 5$  to  $\pm 15$  V, it achieves 10-MHz bandwidth and 0.5-µs set-

tling time to 0.01%. The input offset drift of 1.2  $\mu$ V/1°C and gain drift of 10 ppm/1°C is the lowest of any programmable gain in-amp. Manufactured using the iCMOS process technology, the AD8253 draws just 4 mA of quiescent current and is available in 10-lead MSOP (mini small-outline plastic) packages.

The AD8253 costs **\$4.95** per unit in 1,000-unit quantities.

Analog Devices, Inc. www.analog.com

www.segger.com

# **Embedded IP-PBX**

#### Switch Analog and VoIP Calls

David Rowe describes the design of a  $\mu$ Clinux-powered IP-PBX capable of switching both analog and VoIP calls. With an Analog Devices Blackfin processor, some custom hardware, and Asterisk PBX software, you can build a similar system.

I have always been fascinated with embedded systems and telephony. I really like working "close to the machine" on embedded systems, and I have a parallel interest in speech and telephony that dates back to my ham radio days as a teenager. One project I had been dreaming about for years is an embedded telephony platform for VoIP or IP-PBX applications.

One problem with telephony is that it requires a lot of processing power. Unfortunately, most embedded processors are not too powerful. So, a common design approach for embedded telephony consists of a general-purpose microcontroller combined with a special-purpose DSP chip to handle the hard-core number crunching. This two-CPU approach increases the system cost and complexity.

About 18 months ago, I stumbled across the Blackfin processor from Analog Devices. The Blackfin is a powerful host processor and a DSP (i.e., it can run  $\mu$ Clinux applications and DSP code efficiently and simultaneously on one processor).

A typical embedded processor will struggle to run more than one or two channels of G.729 speech compression or echo cancellation software. The Blackfin, running at 500 MHz, is capable of running 60 channels of G.729 speech compression or echo cancellation. This makes it possible to build low-cost, high-performance embedded telephony systems, like an IP-PBX that can support multiple analog and VoIP channels at the same time. For about \$500, you can now build an IP-PBX with features that only \$10,000 PBXs had a few years ago.

This work is part of the free telephony project (www.rowetel.com/ucasterisk). The goal of the project is to build opensource telephony hardware and software (e.g., an embedded Asterisk IP-PBX) at a low cost. Both the hardware and software are open source. You are free to copy and reuse the hardware designs.

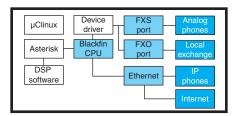

#### **IP-PBX OVERVIEW**

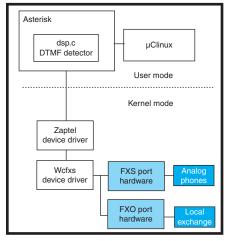

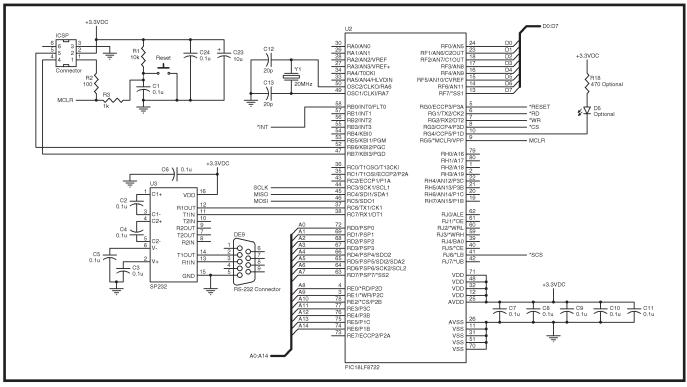

What is an IP-PBX and how does it work? Figure 1 is a block diagram of the embedded IP-PBX that shows the major hardware and software components.

There are two types of analog ports: FXO ports that connect to your local telephone exchange and FXS ports that connect to analog handsets. This jargon can be confusing. The way I remember is the "S" in FXS stands for "station" handset.

The analog ports convert the voice and signaling information to digital signals that the IP-PBX can process.

**Figure 1**—This is a block diagram of the Embedded IP-PBX showing the major software and hardware components. The heart of the system is the Blackfin processor. This is connected to hardware such as the FXO/FXS telephone ports and Ethernet. The Blackfin processor runs the μClinux operating system and Asterisk application software. Examples of signaling information are the ring detection and on/off hook status signals. Analog ports are surprisingly difficult to build because they use a mixture of rather old technologies. For example, a ring signal may be 200  $V_{pp}$  (at low current), on and off hook status is indicated by loop current flowing, and the transmit and receive audio is mixed together on just two wires, which leads to echo problems. All of this must be reliably and safely connected to low-voltage digital systems. Fortunately, there are excellent chipsets available to help build costeffective and reliable analog interfaces.

Telephone calls can also flow through the Ethernet port using VoIP. Both local (e.g., using SIP phones) and trunked calls can be performed using VoIP. The magic of an IP-PBX is that analog and VoIP calls can be tied together. You can route a call from an analog handset over the Internet to save money on long-distance calls.

What happens when you make a regular analog phone call? First, pick up an analog phone's handset. This generates an "off-hook" event in the FXS port that tells the Asterisk software to generate a dial tone in your phone. When you dial 9, DSP software decodes the DTMF tones and presents Asterisk with the digit. Asterisk then connects your FXS port to an FXO port so you can reach the local exchange where you can dial a phone number as usual.

What about VoIP calls? Well, say you use the same analog phone to make the call, but this time you dial

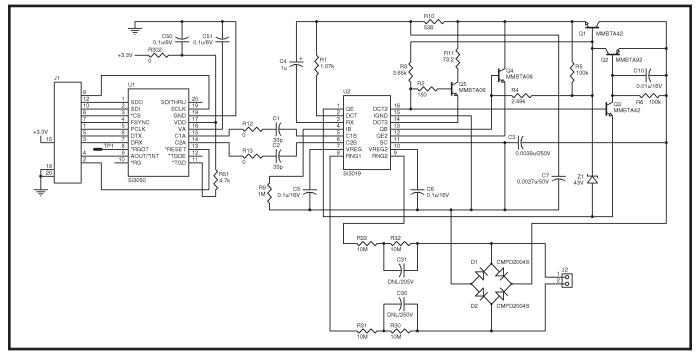

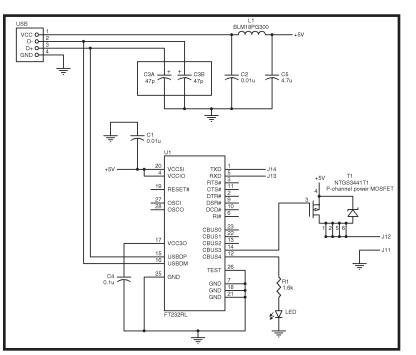

Figure 2—Take a look at the FXO module schematic. It provides an interface between a telephone line and the Blackfin processor. Its most important task is to provide high-voltage isolation, which is achieved using the capacitive barrier formed by C1 and C2.

long distance. In this case, Asterisk is programmed to route the call over the Internet. To save bandwidth, the DSP software compresses the speech samples from the FXS port from 64 kbps down to 8 kbps. The Asterisk software then puts the speech samples in packets and squirts them out the Ethernet interface onto the Internet.

A lot of the IP-PBX's power is provided by the Asterisk software, whose primary sponsor is Digium. The ability to run a powerful operating system such as  $\mu$ Clinux is also very useful. For example, you can telnet into the IP-PBX

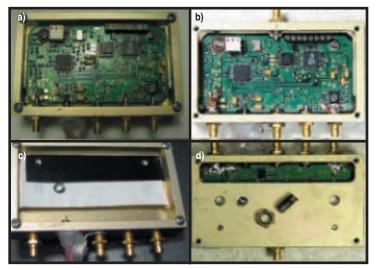

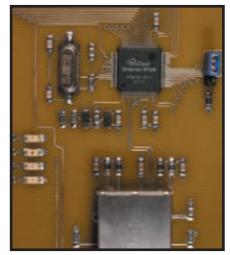

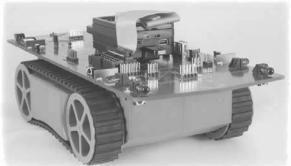

Photo 1—Here you see the 4fx daughter board and modules before assembly. Each of the four modules at the bottom mate with matching connectors in the middle of the 4fx daughter board. Note the large vacant area in the middle of the PCB. It is necessary to provide physical isolation between the FXO ports and the rest of the system.

while it is running to debug and configure it.

#### THE HARDWARE

The hardware is built around four PCBs. The first board is an Analog Devices Blackfin STAMP card. It is a development system that is available offthe-shelf from Digi-Key. It contains an Analog Devices ADSP-BF537 Blackfin chip, 64 MB of RAM, 4 MB of flash memory, and connectors that break out many of the ports. It runs µClinux and is supported by www.blackfin.uclinux.org.

One great feature is that an openhardware/software community exists around the Blackfin. Reference designs for Blackfin hardware (such as the STAMP boards) and various daughter boards are freely available.

On top of the STAMP sits a 4fx daughter board. (Why are boards always girls?) It holds some glue logic and sockets for the modules and also supports an MMC to provide extra flash memory storage. The 4fx's name comes from the fact that the daughter board can support up to four FXS or FXO modules.

The modules are the little boards that plug into the daughter board. There are two types of modules, FXS and FXO. Photo 1 shows the 4fx daughter board and modules disassembled. There are two modules of each type in the photo. Photo 2a features

Photo 2a—The IP-PBX is assembled and configured for four analog ports. From top to bottom, you can see the FXS/FXO modules, the 4fx daughter board, and the BF537 STAMP. There is an optional MMC connector on the left. Green indicates an FXS port, red an FXO. b—The design is expandable to multiples of four ports by stacking additional daughter cards and modules. The wcfxs device driver automatically detects the number and type of ports available. In this case, there are four FXS and four FXO ports.

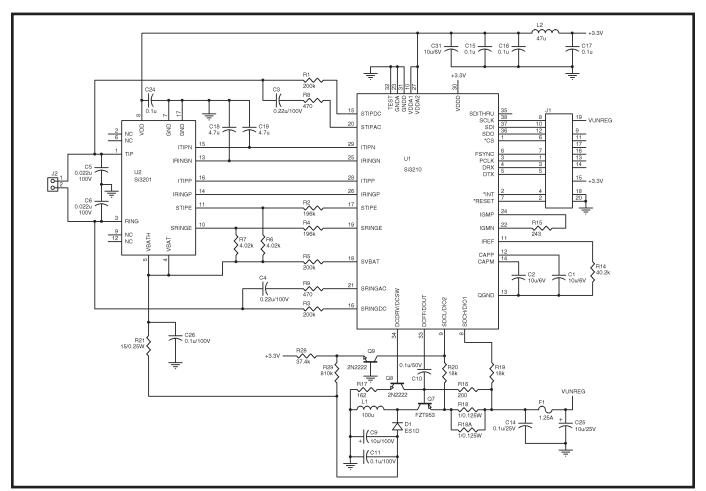

Figure 3—Take a look at the FXS module schematic. It provides an interface between a telephone and the Blackfin processor. The DC/DC converter in the lower-right corner generates 48-V battery and 200-V<sub>pp</sub> ring voltages from a standard 12-V supply.

the entire system assembled, powered up, and ready to make calls. There are two FXS modules on the left and two FXO modules on the right. The color of each LED indicates the type of module inserted via an autodetection algorithm. It is also possible to stack multiple 4fx boards to expand the number of channels that can run on the system (see Photo 2b).

In the next few sections, I'll describe the schematic-level design for the FXS, FXO modules, and the 4fx card. The Blackfin STAMP card schematics are available at www.blackfin.uclinux.org.

#### FXO AND FXS MODULE DESIGN

The gEDA suite of GPL electronic design automation tools was used for schematic entry, PCB layout, and Verilog simulation throughout the project (www.geda.seul.org). The use of opensource tools makes it easy for anyone to modify the designs. Because the hardware designs are "open," it is nice to use open-source tools where possible. The schematics for the FXS and FXO modules are shown in Figures 2 and 3. Both modules are based on chipsets from Silicon Laboratories. The circuit designs for the modules are derived from the reference circuits provided in the Silicon Laboratories datasheets.

The most important function of the FXO module is to isolate the "line side" of the port from the low-voltage digital side. There are safety reasons for the isolation. If lightning hits the phone lines, you will want a degree of physical isolation between the phone line and the rest of the hardware. This isolation is rigorously tested during FCC-68 compliance testing by the application of high voltages that simulate lightning. The Silicon Laboratories chips achieve it with a capacitive isolation barrier (C1 and C2). The Silicon Laboratories Si3050/Si3019 chipset used for the FXO module also performs other functions, such as line voltage and current monitoring, impedance matching, A/D

and D/A conversion of the speech signal, ring detection, and DC termination.

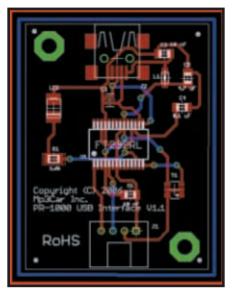

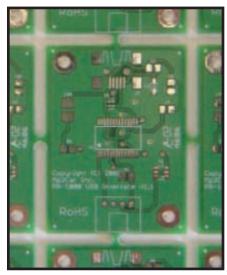

A screenshot of the PCB layout for the FXO module is posted on the *Circuit Cellar* FTP site. The PCB measures about  $50 \times 25$  mm. Note the "isolation barrier" between the two chips, which only C1 and C2 are allowed to bridge. The PCB layout was carefully designed to keep the line side and low-voltage side physically isolated by a 3- to 4-mm gap. Even the ground plane is absent in this area, because it would violate the physical isolation requirements.

The FXS module has similar functions to the FXO module (see Figure 3). In this case, the Silicon Laboratories Si3210/Si3201 chipset is used. The main difference with the FXS module is that it generates ring and "battery" DC supply voltages. Silicon Laboratories employs a clever switched-mode power supply that is modulated to generate the 200- $V_{pp}$  sinusoidal ring voltage. Although the datasheets

# WIZnet iEthernet

#### DESIGN CONTEST

# Witte Section . 60111S Witte

# Put your creativity to the test! (Sep. 20 ~ Jan. 31)

#### Join the Ethernet Revolution!

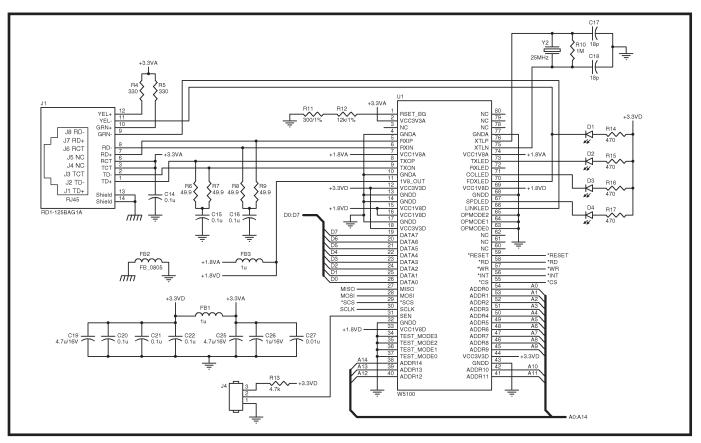

Circuit Cellar magazine is pleased to bring you the WIZnet iEthernet Design Contest 2007. Now you can easily add Ethernet capability to your embedded project and win fame and fortune in the process. WIZnet's W5100 hardwired TCP/IP Ethernet controller will be the key to your contest success. This 3-in-1 chip solution brings TCP/IP implementation without an OS. Both MAC and PHY are embedded.

Show us how you use the impressive W5100 to usher your embedded project into the Ethernet revolution. Your creativity and design skills could win you a share of \$15,000 in cash prizes and recognition in Circuit Cellar magazine.

#### For details, visit www.circuitcellar.com/wiznet.

www.wiznet.co.kr www.ewiznet.com

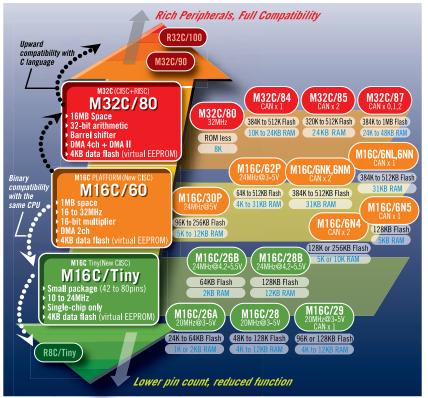

# M16C- The broadest platform with true code and pin compatibility

42 to 144pin, 24K to 1M Byte Flash & 1K to 48K Byte RAM

# **Renesas Technology**

#### No.1\* supplier of microcontrollers in the world

presents a wide range of M16C microcontrollers. M16C is the only fully codecompatible platform in the industry that addresses the entire 8-bit through 32bit price/ performance application space.

Your application can range between 24K Bytes and 1M Bytes of code size, with between 42pins and 144pins of package size, while keeping the same code base and development tools.

The consistency and compatibility of the M16C Platform enables you to reduce your development time while still allowing the flexibility to adapt to changing system requirements.

#### M16C Product Roadmap

#### HOT Products M16C/29 Group

#### M16C/29 Block Diagram

|                             | PLL                 | TimerA 5ch                  |  |

|-----------------------------|---------------------|-----------------------------|--|

| M16C/60<br>CPU Core         | On-Clip Osc         | TimerA 3ch                  |  |

| 20MHz                       | RTC 32KHz           | Three-phase                 |  |

| Multiplier                  | WDT                 | Motor Cont.                 |  |

| Interrupt                   | CRC                 | ROM Correction              |  |

| RAM Max 12KB                | 10-bit A/D Max 27ch | SIO/UART 3ch                |  |

| ROM Max 128KB<br>MASK/Flash | IC/OC timer 8ch     | SIO 2ch                     |  |

| with Protection             | LVD                 | Multimaser I <sup>2</sup> C |  |

|                             | DMAC                | CAN2.0B 1ch                 |  |

#### **Top Reasons To Select M16C**

- **Broad Platform** Wide range of selection; 24KB to 1MB on-board Flash, 42pin to 144pin

- **Compatibility** Pin and Code compatibility across the platform enables you to upgrade/downgrade MCU in same package

- without changing the board design and peripherals.

Powerful High speed interrupts (M32C: 0.61u sec in 32MHz), optimized instructions for 1cycle operations, Hi-speed hardware multiplier.

- Versatile Specialized on-chip peripherals; CAN, LIN, 3ph-PWM, DMA, etc

- Efficient Multiple clock sources and multiple power saving modes

- Quiet Built-in noise cancellation circuits provides excellent EMI/EMS characteristics that outperform IEEE standard spec

- Easy Same Tool Chain for evaluation and development across the board

- Reliable and secured Trusted flash and built-in fail safe features such as oscillation-stop detection circuit, protect registers, enhanced WDT, etc.

Source: Gartner(March 2007) "2006 Worldwide Microcontroller Vendor Revenue" GJ07168

#### Get Started Today -

Go online and register to be eligible for a FREE Starter Kit www.america.renesas.com/ReachM16C/d

RenesasTechnologyCorp.

claim that the DC/DC converter can work well down to 5 V, I found that a 12-V supply was required for the DC/DC converter to avoid excessive analog noise.

The Si3210/Si3201 FXS chipset also takes care of other functions, such as line voltage monitoring, loop current detection, overload protection, impedance matching, and A/D and D/A conversion of the speech signal.

The FXS module's PCB layout is quite challenging because there are three distinct signal areas in the small  $50 \times 25$  mm area. (A screenshot of the FXS module PCB is posted on the Circuit Cellar FTP site.) The first area handles line-level analog signals from the telephone handset. The second region is a digital interface containing a 2.048-MHz TDM bus and a SPI bus that connects to the fast rise time (i.e., noisy) signals from the Blackfin. The third area is a switchmode DC/DC converter that converts a low-voltage 12-VDC rail to the -90 VDC required for the telephone "battery" supply and also generates the 200- $V_{pp}$  ring voltage. To generate the high voltages at even small currents, large pulsed currents must flow in the 12-VDC supply line, which is a potential source of noise.

It is important to prevent the DC/DC converter and digital side from injecting noise into the sensitive low-level analog section. Based on tips from the Silicon Laboratories application notes, a few tricks were used. The DC/DC converter ground was kept isolated from the ground plane and connected only at a single point. This prevents large ground current spikes from entering the ground plane. Large current pulses in the ground plane get converted to voltages (because the ground plane impedance is small but nonzero), which then get superim-

| A2 | A1 | A0 | SPI Device         |

|----|----|----|--------------------|

| 0  | 0  | 0  | nCS0: spare        |

| 0  | 0  | 1  | nCS1: Port 1       |

| 0  | 1  | 0  | nCS2: Port 2       |

| 0  | 1  | 1  | nCS3: Port 3       |

| 1  | 0  | 0  | nCS4: Port 4       |

| 1  | 0  | 1  | nCS5: LED register |

Table 1—This truth table relates addresses to the SPI device that you are currently talking to. Note that only five devices are decoded. Four of the devices are FXS/FXO modules. Device 5 is a bank of bicolor LEDs.

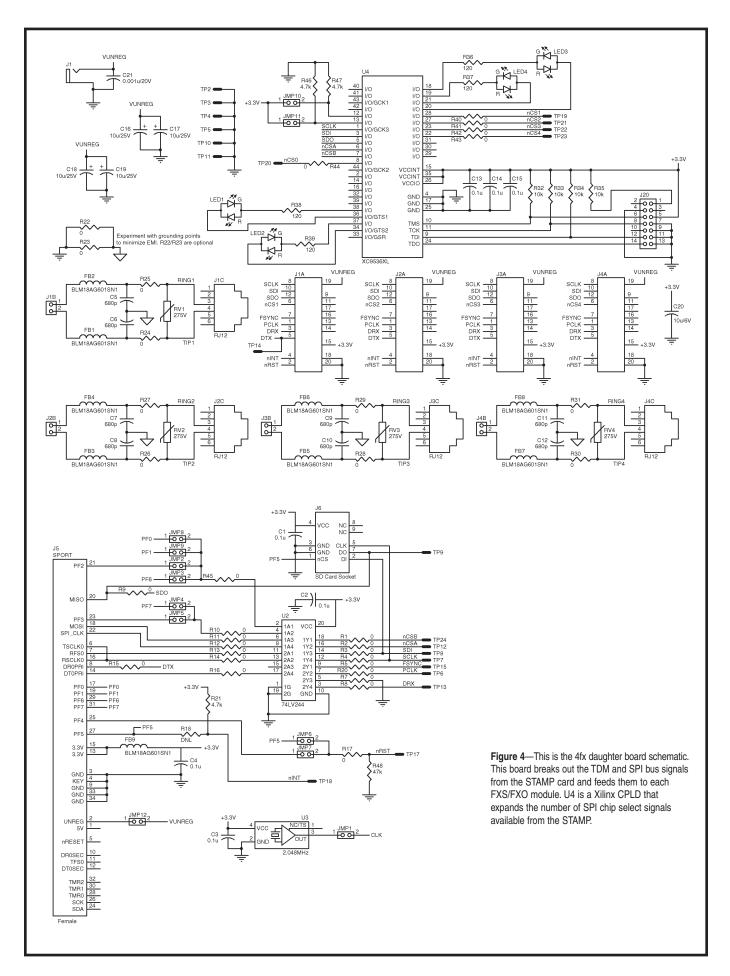

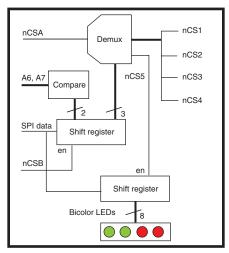

Figure 5—The CPLD expands the number of SPI chip select lines available using a demultiplexer and shift register. It also implements a SPI peripheral that drives the bicolor LEDs.

posed on the low-level analog signals as unwanted noise. You can see the lack of a ground plane in the upper-left hand part of the FXS module PCB screenshot on the *Circuit Cellar* FTP site.

A ground plane was used throughout the analog section and in the digital section. The two ground planes are connected only at a single point to prevent digital currents from flowing through the analog section and inducing noise. This point is as far away from the DC/DC converter as possible.

Bringing the two module designs to life was surprisingly straightforward. The first FXO module I built had some problems with clicks and pops in the audio; however, a good cleaning with the flux remover fixed that! The flux I use is conductive so any residue tends to upset circuits that depend on high-resistance values in certain areas.

I then tried the FXS module and it worked on the first try. I was really happy about that. I was placing calls about 5 minutes after I applied power. Hardware development isn't meant to work like that!

#### 4fx DAUGHTER BOARD DESIGN

Now, take a look at the 4fx daughter board schematic (see Figure 4). The FXO and FXS modules communicate with the host processor via two serial buses. The signaling and control data flows via a SPI bus. The actual transmit and receive speech samples flow on a time division multiplexed (TDM) bus.

The 4fx breaks out the SPORT connector from the STAMP board and feeds the SPI and TDM signals to each module. Because the STAMP has only a limited number of SPI chip-select signals available, a Xilinx CPLD (U4) is used to expand the number of SPI devices that can be addressed. This is described in the next section. The CPLD also supports a "stacking" architecture where several boards can be stacked on top of each other to obtain extra analog ports.

To reduce EMI, the suppression components (e.g., ferrites and capacitors) for each port were placed on the daughter board as close as possible to the RJ-11 connectors. Each digital line in the daughter board also has series termination resistors. The resistors are initially loaded as  $0 \Omega$ , but this can be increased to combat EMI or ringing issues if required. A 74LV244 buffer (U2) is also used to reduce the edge rates of high-speed digital signals from the Blackfin STAMP card. Reducing the edge rates reduces EMI because slow rise and fall times mean reduced high-frequency energy.

#### XILINX CPLD FIRMWARE

On the 4fx card, a Xilinx CPLD is used to expand the number of SPI select lines available and provide a register to drive the LEDs (see Figure 5).

The STAMP SPORT connectors have only a limited number of SPI select lines available. However, on the 4fx design, I have many SPI devices (e.g., four telephony ports and a register to drive the LEDs). I would also like to stack the 4fx cards to build eight port telephony systems. So, the problem is accessing multiple SPI devices across multiple cards using only a small number of SPI lines available on the SPORT connector.

| D1 | D0 | LED1  |

|----|----|-------|

| 0  | 0  | Off   |

| 0  | 1  | Red   |

| 1  | 0  | Green |

| 1  | 1  | Off   |

Table 2—This is a truth table for LED status. Two digital lines are used to drive each LED, which enables you to select the polarity as well as switch the LED off and on.

# The Newest Semiconductors

AIMEL

RAMTRON

(BOURNS'

POWER

The ONLY New Catalog Every 90 Days

Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 335 leading suppliers.

a tti company The Newest Products For Your Newest Designs

(800) 346-6873

Over 860,000 Products Online

www.mouser.com

I decode a large number of SPI devices using two SPI select lines called nCSB and nCSA. nCSB is asserted and a byte is sent that selects the SPI device you want to address. The format is:

D7 D6 D5 D4 D3 D2 D1 D0 A7 A6 X X X A2 A1 A0

A [7:6] selects the card from other cards in a stack. Two jumpers determine the address of the card. Each card in the stack must have a unique 2-bit address to be successfully decoded. A [2:0] selects the SPI device on the card (only five devices are decoded) (see Table 1).

nCS [4:1] is routed via I/O pins to devices external to the CPLD. nCS5 is an internal SPI device and is not routed to an I/O pin. Once the SPI device has been selected, nCSA is asserted to talk to the actual SPI device. nCSA may be asserted as many times as required (e.g., to perform a block transfer on the SPI device).

Note that once the device has been selected, SPI transfers proceed normally (i.e., assert nCSA and read/write as desired). When access to another SPI device is required, nCSB is asserted and the byte sent can be used to select another device (or card).

The LEDs appear as an 8-bit SPI register at address five on the card. When you write to the register, the value determines the status of each

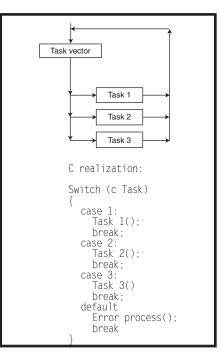

Figure 6—The IP-PBX runs the µClinux operating system and Asterisk PBX software. To run Asterisk on the Blackfin, the DTMF detector was modified to use fixed-point arithmetic. The wcfxs FXS/FXO port device driver was also modified to support the Blackfin serial port and SPI hardware. Listing 1—Take a look at the floating-point DTMF detector inner-loop code. This is the core of a DTMF tone detector. It executes 64,000 times for every channel running on the IP-PBX. The final line implements a typical DSP operation: multiply two numbers and then add and subtract from the result.

```

static inline void goertzel_sample(goertzel_state_t *s, short sample)

{

float v1;

float fsamp = sample;

v1 = s->v2;

s->v2 = s->v3;

s->v3 = s->fac * s->v2 - v1 + fsamp;

}

```

Listing 2—This is fixed-point DTMF detector inner loop code. The DSP operation has been broken down into two lines. Note the casting to 16-bit integers and scaling via shifts. These operations give you fine control over how the C compiler treats these operations. The main challenge with fixed-point DSP is keeping the dynamic range of signals inside a 16-bit range.

```

#define AMP_SCALE 8

#define FAC_SCALE 14

static inline void goertzel_sample(goertzel_state_t *s, short sample)

{

int16_t v1_fix;

int mpy;

v1_fix = s->v2_fix;

s->v2_fix = s->v3_fix;

mpy = (int16_t)( ((int)s->fac_fix * (int)s->v2_fix) >> FAC_SCALE );

s->v3_fix = mpy - v1_fix + (sample>>AMP_SCALE);

}

```

LED (see Table 2). And similarly for the other LEDs:

D[3:2] LED2 D[5:4] LED3 D[7:6] LED4

#### SOFTWARE

The Silicon Laboratories chips are commonly used with Asterisk on PCIcard-based line interface hardware. Open-source drivers for the chips exist, dramatically simplifying development.

Figure 6 shows the software architecture of the Asterisk implementation used for the embedded IP-PBX. Asterisk is a user-mode application that communicates with a kernelmode driver called zaptel. Zaptel communicates with lower-level drivers that talk to the actual hardware.

The Asterisk wcfxs driver was chosen as the starting point for the embedded IP-PBX. The driver was originally written to communicate with the Silicon Laboratories chips operating on a PCI bus. To port the driver to the Blackfin, the PCI interface component was carefully removed and replaced with code that interfaces to the Blackfin's SPORT (TDM serial port) and SPI hardware.

Surprisingly, it is actually easier (and cheaper) to interface the Silicon Laboratories chips to the Blackfin compared to an x86 PC because no PCI bridge is required. The driver is also simpler.

Most of the software changes were confined to the wcfxs driver, although some changes to the Asterisk application were also required, such as architecture-specific word-alignment issues and several Linux-µClinux porting issues. One area that needed optimization was the DTMF detection routines. The code was written to run on a general-purpose x86 CPU where it is assumed floating-point support is available in the form of a hardware floating-point unit (FPU). The Blackfin does not have an FPU and is in fact optimized for fixedpoint operation. Thus, the original float DTMF code ran very slowly, consuming 31 MIPS per channel.

The problem was traced to the "inner loop" of the DTMF detector (see Listing 1). The code implements a digital filter and is called eight times for each input sample (eight filters are required for each DTMF detector). Because each channel has 8,000 input samples per second, the total number of function calls is  $8 \times 8,000 \times$  the number of channels per second. So, it is important to make sure the "inner loop" code runs as efficiently as possible.

The trick is to replace the floatingpoint code with equivalent fixed-point code (see Listing 2). The code maps directly to the assembler instruction set of the Blackfin and compiles down very efficiently. The scale factors were chosen to keep the dynamic range of the variables within a range easily represented by a 16-bit integer. The fixedpoint port was tested with a unit test from the Spandsp library that puts the DTMF detector through its paces (www.soft-switch.org).

The result was that the fixed-point DTMF detector worked just as well as the floating-point version, but it consumed about 1.75 MIPS compared to the 31 MIPS required for the floating-point version. Standard vanilla C code was used (see Listing 2). With a little Blackfin assembler replacing the C code, the performance could be improved even further. However, with 500 MIPS available on the Blackfin, 1.75 MIPS for the DTMF decoder is probably fast enough.

#### **GO BUILD**

In this article, I explored the architecture of an embedded IP-PBX and described in detail the schematic-level hardware design and PCB layout. Using embedded techniques and opensource hardware and software, it is possible to build a low-cost IP-PBX with features (VoIP, IVR, and flexibility) that rival those of \$10,000 PBXs.

Other areas of the project that have not been mentioned due to space limitations include the Asterisk software configuration, a custom DSP motherboard and configuration of the PBX. For more information, visit the project web site (www.rowetel.com/ucasterisk).

The software and hardware designs for the project are open-source and contributions by corporations or individuals are welcome. Currently, a team of companies and individuals is working on the project in areas like DSP, µClinux software, and hardware development. Refer to the project web site for more information.

If you would like to get started with embedded IP-PBX development, I have a fully assembled and tested IP04 IP-PBX for \$450 plus shipping.

Author's Note: Thanks to the Linux, Blackfin, Asterisk, and gEDA communities. My wife Rosemary did a great deal of the schematic entry for the FXS module, and Jerry Zeng from Analog Devices was very helpful in checking the design and brainstorming the CPLD requirements for the 4fx.

David Rowe has 20 years of experience in the development of DSP-based telephony and satellite communications hardware/software. He has a wide mix of skills, including software, hardware, and project management. He earned a Ph.D. in DSP Theory. David has held executivelevel positions in the satellite communications industry (www.dspace.com.au) and has built and successfully exited a small business (www.voicetronix.com). However, he has decided that he is better at debugging machines than people, so he currently hacks telephony hardware and software full time.

#### **PROJECT FILES**

To download code, go to ftp://ftp.circuit cellar.com/pub/Circuit\_Cellar/2007/208.

#### RESOURCES

Blackfin Linux Project, www.blackfin. uclinux.org.

gEDA Project, www.geda.seul.org.

D. Rowe, "Free Telephony Project: Open Embedded Telephony," 2007, www.rowetel.com/ucasterisk.

S. Underwood, "Spandsp Project," www.soft-switch.org.

#### SOURCES

**Blackfin STAMP** Analog Devices, Inc. www.analog.com

Si3050/Si3019 and Si3210/Si3201 chipsets Silicon Laboratories, Inc. www.silabs.com

# NimbleSig

A Compact DDS RF Signal Generator

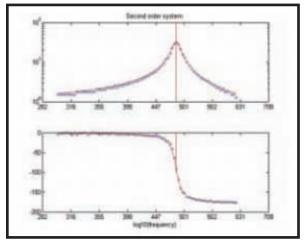

The NimbleSig is a versatile DDS RF signal generator built around a Luminary Micro LM3S811 microcontroller. This handy system, which provides a frequency-agile RF output signal source with 1-Hz step resolution, is also capable of low-level (–50 to 10 dBm) RF power measurement.

Modern integrated circuits make the generation of stable RF signals a relatively trivial chore compared to the technology of earlier times. Typical 1960s-era VHF signal generators were relatively huge (about the size of carry-on-luggage) and somewhat impractical to use because of poor frequency stability. The manual process of tweaking the signal to within 1000 Hz of the desired frequency took some tedious fine-tuning. The low-level RF power meters of that era often needed to be renormalized to zero every few minutes.

With current technology, it is now possible to construct a shirt-pocketsize VHF/RF signal source/power meter module that maintains 10-Hz stability at room temperature for days on end and can be readily shifted in frequency in 1-Hz step increments. It takes only one additional IC to add a stable RF power meter capable of measuring levels lower than a nanowatt. The \$100 component cost for such a modern-day, dualfunction module seems like a technoeconomic boon when you consider the performance and original cost of legacy RF test equipment. RF instrumentation is yet another area of technology where there have been huge improvements during the past few decades.

From the introduction of relatively low-priced direct digital synthesis (DDS) and logarithmic RF detector ICs, I have built various low-cost RF signal sources and detectors based on new semiconductors as they have become available. During the past decade, I have witnessed a lot of improvement in DDS technology. The maximum output frequency of my first DDS generator was limited to about 20 MHz. Current technology now supports 10 times that. Recently developed DDS ICs that are capable of generating 400-MHz signals are now becoming available at more attractive costs as technology continues to evolve.

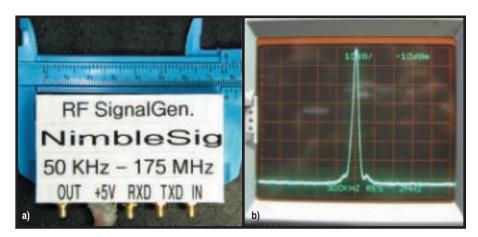

In this article, I will describe a DDSbased RF signal generator/level detection module. It is intended to be used either with a PC as a signal generator or integrated into equipment that requires an integral RF signal source. I named the module NimbleSig for its quick-frequency agility, which enables it to act as a signal source across more than 11 octaves of spectrum (see Photo 1). The NimbleSig design uses a Fox Electronics FOX924B TCXO for a reference oscillator source, which provides good frequency stability. DDS control is provided by a 50-MHz, 32-bit Luminary Micro LM3S811 microcontroller linked to the DDS chip at a data rate of 25 Mbps, which is fast enough to accommodate many modulation needs.

#### **DESIGN & HARDWARE**

My goal for this project was to build a compact, inexpensive, VLF-to-VHF, AM/FM/CW multimode signal generator module that could service the sig-

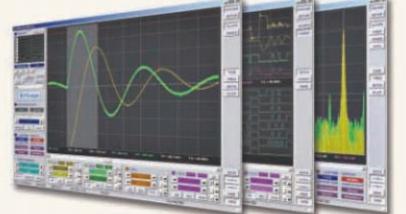

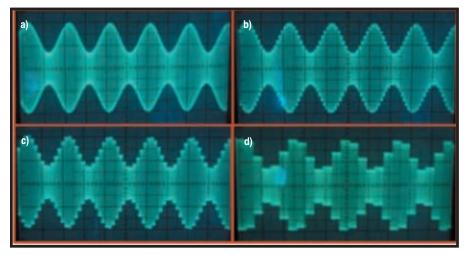

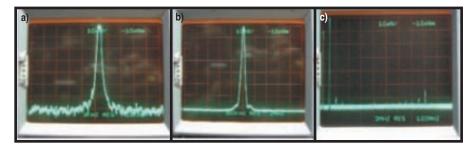

**Photo 1a**—This is the completed NimbleSig module. It is framed with a caliper to illustrate its small size in both English and metric units. **b**—The NimbleSig output spectrum analyzer display spanning 30 to 50 MHz. A 40-MHz full signal is at -10 dBm in the center of the screen.

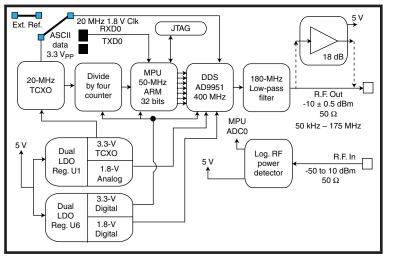

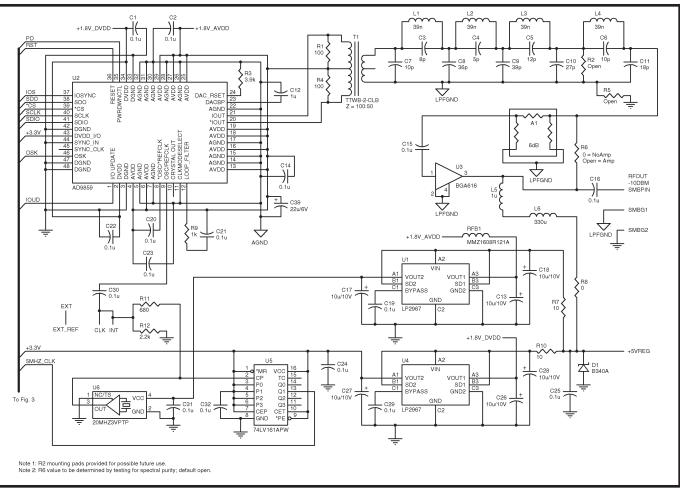

nal source needs of a wide variety of applications. Figure 1 is a block diagram of the hardware. Figures 2 and 3 show the circuitry details.

The RF generator engine uses either an Analog Devices AD9859 or an AD9951 DDS IC. Both chips employ an internal 400-MHz PLL clock, which enables them to generate signals up to about 175 MHz. The compatibility of the two devices gives you a price/performance choice to best match the needs of the intended applica-

Figure 1—This is a block and level diagram of the NimbleSig design. The module is powered by a regulated 5 V. The four onboard regulators provide the voltages needed by the TCXO, divider, DDS, and MPU. The external reference injection and post power amplifier are optional.

tion. The AD9951 can generate a cleaner output spectrum because it uses a 14-bit DAC compared to the 10-bit DAC in the AD9859. Also, the 14-bit resolution of the AD9951 provides finer output-level control over a wider dynamic range, which is usually desirable for a signal generator application. For constant outputlevel applications where the DDS always runs at a maximum output level, the AD9859 might be the best techno-economic choice.

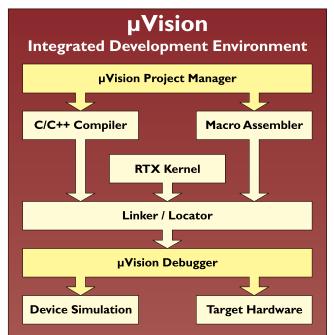

The LM3S811 microcontroller uses a 32-bit ARM Cortex-3 architecture core that runs at 50 MHz, has 64 KB of program memory, and 8 KB of RAM. It also has many peripherals, including the timers, UART, ADC, and SSI blocks needed for this project. Software development for the proces-

sor family is well supported by Keil's μVision IDE, which employs ARM's C compiler. Luminary Micro's low-cost (about \$50) LM3S811 evaluation mod-

Figure 2—The NimbleSig schematic shows the DDS and analog circuitry, which includes a TCXO, a frequency divider, a DDS, 1.8-V/3.3-V regulators, an output low-pass filter, and an optional power amplifier.

ule (EVM) can be used for both MPU programming and firmware debugging. This makes setting up a software development workstation for Luminary Micro's Stellaris microcontroller family easy and inexpensive.

The small FOX924B TCXO was chosen for the 20-MHz frequency reference oscillator. The temperature stability for this device is specified at  $\pm 2$  ppm from -40° to 85°C, which should meet the needs of most applications. An external reference can be used for applications with

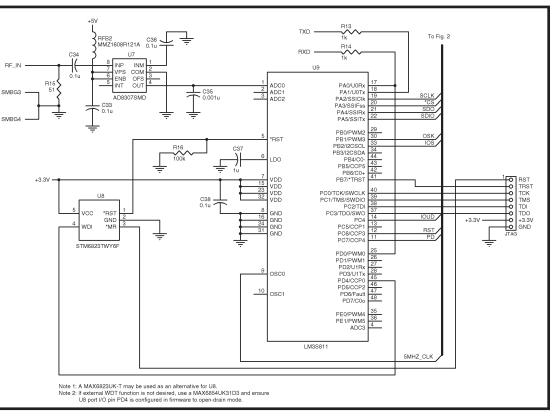

Figure 3—The NimbleSig circuitry schematic shows the MPU, MPU supervisor, power detector, serial UART port, and JTAG interfaces.

more demanding frequency stability and phase noise requirements.

The FOX924B circuit provides two 20-MHz output signals, one at 1.8  $V_{pp}$ and the other at 3.3 V<sub>pp</sub>. The 1.8-V signal is used to provide a clock reference for the DDS. The internal PLL of the DDS multiplies the 20-MHz clock by 20 to achieve an internal clock rate of 400 MHz. The 3.3-V  $_{\rm pp\prime}$  20-MHz output of the FOX924B feeds a low-voltage CMOS counter IC, which divides the frequency down to 5 MHz. This 5-MHz, 3-V<sub>PP</sub> logic signal matches the clock-reference requirements of the LM3S811 for locking its internal 200-MHz PLL, which is internally divided by four to form the 50-MHz microcontroller system clock.

The FOX924B is powered by a dedicated 3.3-V low-noise regulator because noise on its TCXO power would tend to frequency modulate the reference clock, which would degrade the output's spectral purity. For similar reasons, a separate regulator was also provided to supply the DDS chip's analog power bus.

The proven Analog Devices AD8307 logarithmic RF power detector was chosen for the RF power level measurement device. The wonderful detector has a 0- to 500-MHz bandwidth and offers less than  $\pm$ 1-dB tracking error from roughly –75 to 17 dBm. Compensation for the frequency response of the AD8307, which rolls off a few decibels in the VHF band, is accomplished here within the MPU's firmware.

The MPU sets the state of various DDS control inputs with 3.3-V logic from GPIO pins. The MPU's SSI peripheral provides the data communications path to the DDS chip. The SSI peripheral provides a pair of 16-word internal FIFO buffers for both output and input data. The architecture gives the MPU time to efficiently pass data in parallel format to and from the independent SSI.

The communications path to the host controller is provided by the internal UART0 peripheral. The interface passes regular 3-V unipolar data directly from the microcontroller via protection circuitry to the outside world. As the 3.3-V powered LM3S811 has 5-V tolerant I/O pins, the data ports may be directly connected to either 3- or 5-V logic external devices. Design details for my RS-232C adapter, which I use to interface to my PC serial port, can be found in the NimbleSig contest file posted on the *Circuit Cellar* web site (www.circuitcellar.com/designstellaris 2006/winners/1648.html). SMB coaxial connectors similar to the type used for the RF ports are also used for the UART, TXD, and RXD data. Coaxial connections for the data provide shielding for any potential EMI egress or ingress from or to the RF tight Nimble-Sig cast aluminum enclosure.

Programming and debugging the MPU is accomplished via the JTAG port connected to the LM3S811 EVM, which in turn is connected to the development workstation PC via a USB port. The EVM connection to the NimbleSig module uses a custom-made ribbon cable that adapts the JTAG standard 20-pin header to the eight-pin, lower-profile SIP socket used here. The design for this rather simple cable is also described in the contest entry.

As you can see in Figure 1, the DDS chip's output is fed into a 180-MHz low-pass filter, which blocks the 400-MHz clock and the sideband images that are always present in the raw output from a DDS DAC. For example, in the case of generating a 175-MHz signal, there would also be images present at 225 MHz

# BitScope USB Mixed Signal Oscilloscope

#### Analog + Digital

#### **Digital Storage Oscilloscope**

Dual Channel Digital Scope with industry standard probes or POD connected analog inputs. Fully opto-isolated.

#### Mixed Signal Oscilloscope

Capture and display analog and logic signals together with sophisticated cross-triggers for precise analog/logic timing.

#### Multi-Band Spectrum Analyzer

Display analog waveforms and their spectra simultaneously. Base-band or RF displays with variable bandwidth control.

#### Multi-Channel Logic Analyzer

Eight logic/trigger channels with event capture to 25nS.

#### DSP Waveform Generator

Built-in flash programmable DSP based function generator. Operates concurrently with waveform and logic capture.

#### Mixed Signal Data Recorder

Record to disk anything BitScope can capture. Supports on-screen waveform replay and export.

User Programmable Tools and Drivers Use supplied drivers and interfaces to build custom test and measurement and data acquisition solutions.

#### BS100U Mixed Signal Storage Scope & Analyzer

Innovations in modern electronics engineering are leading the new wave of inventions that promise clean and energy efficient technologies that will change the way we live.

It's a sophisticated world mixing digital logic, complex analog signals and high speed events. To make sense of it all you need to see exactly what's going on in real-time.

BS100U combines analog and digital capture and analysis in one cost effective test and measurement package to give you the tools you need to navigate this exciting new frontier.

Standard 1M/20pF BNC inputs

Smart POD Connector

Opto-isolated USB 2.0

12VDC with low power modes

#### BitScope DSO Software for Windows and Linux

BS100U includes BitScope DSO the fast and intuitive multichannel test and measurement software for your PC or notebook.

Capture deep buffer one-shots, display waveforms and spectra real-time or capture mixed signal data to disk. Comprehensive integration means you can view analog and logic signals in many different ways all at the click of a button.

The software may also be used stand-alone to share data with colleagues, students or customers.

Waveforms may be exported as portable image files or live captures replayed on another PC as if a BS100U was locally connected.

# www.bitscope.com

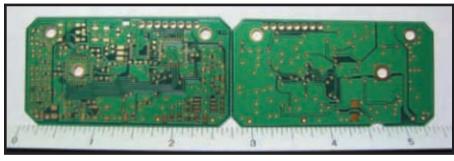

Photo 2—Here are both the component and bottom sides of the NimbleSig revision 2 bare PC board. The large center plated through hole in the center of the DDS footprint is there to enable you to solder the analog ground tab from the bottom side. The triple ground plane isolation is shown in the lower right.

(i.e., 400 - 175) and at 575 MHz (i.e., 400 + 175). The 13-pole elliptic filter design used here has a sufficiently sharp cut-off response to pass 175 MHz and reject frequencies above 225 MHz.

The filter was designed with two excellent freeware filter CAD programs. SVCfilter by Tonne Software was initially used to design a threesection, 180-MHz elliptic LPF. The fourth section was then added and optimized with Linear Technology's LTspice/SwCAD III program. It found that it was possible to use 39-nH coils for each of the four inductors, which simplifies parts procurement.

The graph of the filter response that was plotted by the LTspice/SwCAD III is posted on the Circuit Cellar FTP site. make the inductors a good choice for this application.

The LPF corner frequencies of the two filters I built varied due to component tolerances. One filter limited the flattened (-10 dBm) output range to 174 MHz while the second extended it to 178 MHz.

The output from the low-pass filter may be connected directly to the output connector to provide a maximum output level of about -5 dBm or the signal can be boosted by an optional 18-dB amplifier. The optional amplifier can provide additional output power for driving passive mixers, which typically need 7-dBm local oscillator drive levels. However, for applications that require a clean spectrum, the amplifier is not a desirable

option because the harmonics it generates significantly degrade the relatively clean spectrum from the DDS.

The NimbleSig module is designed to be powered from an externally regulated 5-VDC power supply. The externally regulated 5-V bus is used directly to power the AD8037 logarithmic power detector and the optional MMIC amplifier.

Thanks to Analog Devices's lowvoltage design of its DDS cores, the NimbleSig ICs do not dissipate much power. A ground tab centered under the DDS chip provides adequate heat conduction as well as a good ground connection to the PCB's analog ground plane. The DDS chip runs barely warm to the touch.

Specific DDS chip datasheets for the ICs employed here and various associated application notes on DDS-related topics are available in the RF/IF components section of the Analog Devices web site. A more detailed componentlevel description of the NimbleSig's circuitry is available on the Circuit Cellar FTP site.

#### ASSEMBLY

The component and bottom sides of the PC board are shown in Photo 2. The artwork is designed to an 8-mil clearance specification and the PCB

stock is 1/32" FR10.

The PC board has three distinct, mutually isolated ground planes, which result in improved noise performance. The largest ground plane that extends to the left end of the board is the digital ground. The area in the center with the large plated through hole under the DDS footprint is the analog ground. The third ground plane on the right is the filter ground.

The solder pads are gold plated. Note that a silkscreen with component designations was omitted due to resolution limitations of the design software. Because the font sizes were too large, there was insufficient room on

The cut-off is quite sharp with the first null in the reject band around 230 MHz. The attenuation at 225 MHz is about -55 dB relative to the insertion loss at 175 MHz. Thus, the 225-MHz image (i.e., 400 - 175) is well attenuated even with the DDS operating at the maximum intended frequency limit of 175 MHz.

The minuscule, surfacemount component size 0603, 39-nH inductors (made by Murata Manufacturing) used here within the filter circuit have a minimum Q specification of 40 near the 180-MHz cutoff frequency. The Q increases to about 90 at 1 GHz with self resonance at 2.8 GHz. These characteristics

Photo 3a-The populated PCB is mounted in the chassis of the NimbleSig assembly prior to the installation of the shielding braid. b-The assembly has an external reference injection jack at the top and the RF shielding braid covers the center pins of the input/output jacks (jacks on the opposite bottom corners). c-The plastic sheet bottom isolation barriers are shown with the protruding solder bulb tip of the brass analog-ground-post screw, **d**—The brass ground post set screw has been removed, the soldered analog ground-plated through hole can be seen below the tapped screw hole, and the ground braid bonding of the triple ground planes is soldered to the threads of the gold-plated RF connectors.

the board to clearly label the components without masking the solder pads. As a better alternative, a blowup pictorial of the silkscreen layer was used for component position reference during construction.

The plated through hole in the center of the DDS footprint enabled me to solder the analog ground tab of the DDS chip from the bottom side after I finished the component-side soldering. A brass set screw threaded through a tapped hole in the chassis provided a low-impedance chassis connection to further improve analog grounding (see Photo 3).

The RF detector IC is positioned in the lower-right corner of the board to provide maximum isolation from the DDS FRF output circuitry. The detector is surrounded by ground planes on both sides of the board, which tends to reduce stray RF coupling to the detector from the rest of the circuitry. Mounting pads for the polarity protection diode can be seen on the bottom of the board near the power injection input area.

The component area on the extreme left end of the PCB is the lowpass filter area. The DDS chip is to the right of the LPF section (see Photo 3). The rows of DDS pins on the left and bottom sides (pins 25–48) mainly carry the control signals between the MPU to the IC. The reference clock is injected on the right row (pins 1–12) and the output is taken from the top row (pins 13–24). Power and ground gets applied to multiple pins in all of the rows. The two 1.8-V power buses essentially circle the perimeter of the IC.

A fiber washer is used under the left mounting screw to ensure filter ground plane isolation is not compromised. Mylar insulation barriers are placed under the PCB to ensure the electrical isolation of the bottom side of the PCB from the chassis. The three ground planes are bonded together and grounded to the chassis via the body

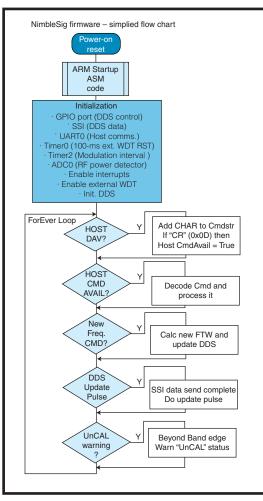

Figure 4—This is a simplified firmware flowchart of the NimbleSig firmware. The initialization routines and "forever" loop are in the main flow. On an exceptional basis, host commands are accumulated, checked, and processed. New frequency tuning words are calculated and update DDS I/O control pulses are sent when needed.

of the RF output SMB connector. A glimpse of the bonding braid can be seen in the bottom left below the corner of the PCB. The RF output and input connector center pins are partially shielded with an umbrella of braid.

The Coilcraft wideband output coupling transformer is within the white enclosure above the DDS chip. The TCXO is located to the right of the transformer. The pad for injection of an external reference is positioned along the edge to the right of the TCXO.

The JTAG connector is the eight-pin SIP socket along the edge above the MPU. Ground pin 8 is closest to the corner of the board. The 3.3-V power bus pin 7, which is not needed for the EVM, should be covered with a small piece of electrical tape. The removal of the mating pin on the ribbon cable completes a connector key.

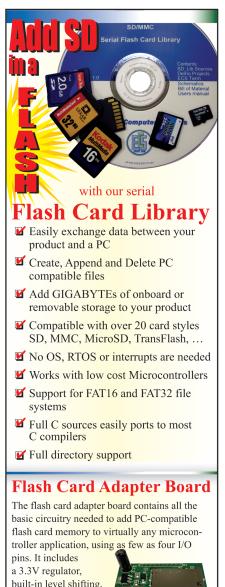

a 3.3V regulator, built-in level shifting, and sockets for both SD/MMC and MicroSD/TransFlash memory cards.

#### **Development Board**

The development board includes a built-in demo application and all the necessary hardware to run each of the example programs

included with the SFCLIB (sold separately). It includes sockets for SD/MMC and MicroSD/TransFlash memory cards.

More information at: WWW.ECS87.com/sfclib 603-776-3151 • 5 Emerson Drive Center Barnstead, NH 03225 The divide-by-four-counter IC is located on the left of the MPU. The digital power bus dual-3.3-V/1.8-V regulator is located near the power input port below the DDS IC. The analog power bus dual 3.3-V/1.8-V regulator is located on the right end of the PCB above the Analog Devices AD8307 RF power detector IC. Although the regulators perform well, they are tiny! They are difficult to solder without an oven because of the grid array-type, leadless package.

The mounting pads for the optional

RF output amplifier chip and associated components can be seen in the bottom-left corner close to the RF output connector. Photos 3a and 3d show the grounding braid used to shield the center pins of the RF connectors. This improves the dynamic range of the RF detector and reduces the coupling of the 100-MHz synchronization clock spur into the output spectrum.

#### FIRMWARE

The NimbleSig firmware was written

)0-858-8355

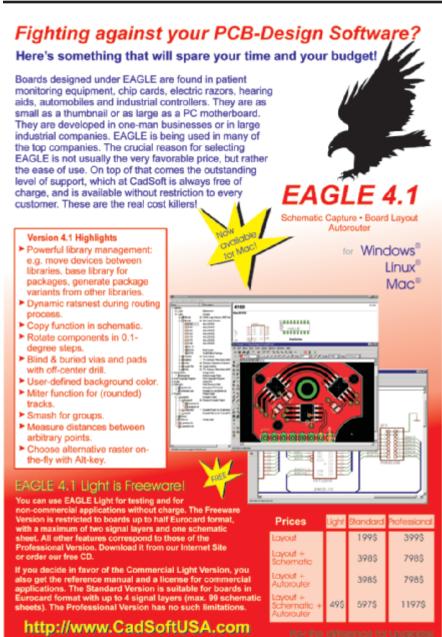

CadSoft Computer, Inc., 801 S. Federal Highway, Delray Beach, FL 33483 Hotline (561) 274-8355, Fax (561) 274-8218, E-Mail : info@cadsoftusa.com within the restraints of the free, noncommercial, evaluation version of the Keil  $\mu$ Vision IDE, which is limited to a maximum program size of 16 KB. As I write this article, the code size is about 11 KB. Thus, there is still room to add more features. However, the commercialization of the design or the expansion of the NimbleSig code beyond the 16-KB limit would require the licensing of Keil's  $\mu$ Vision IDE.

The LM3S811 MPU provides sufficient onboard processing power to accurately and quickly calculate the 32-bit frequency tuning words (FTWs) with 64-bit arithmetic. The high-level C code and large program memory makes the provision of a plain-language, command-prompt-style user interface easy to implement.

The NimbleSig MPU controls the output frequency of the DDS by first calculating and then sending a 32-bit binary number called the FTW to the appropriate DDS control register. The output frequency from the DDS depends on the DDS's internal clock frequency and the value of the FTW. The FTW is calculated by the LM3S811 MPU:

#### $FTW = 4,294,967,296 \times \frac{FreqO}{ClkRef}$

FreqO is the desired output frequency and 4,294,967,296 is  $2^{32}$ . ClkRef is the exact frequency of the reference clock, which in this case is TCXO frequency × 20 = 400,000,000 ±calibration.